1 Tujuan

a. Mampu mengaplikasikan Generic Array Logic

b. Mampu membuat rangkaian Generic Array Logic

c. Mampu mensimulasikan dengan proteus

1. gerbang logika AND

Gerbang AND memerlukan 2 atau lebih Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang AND akan menghasilkan Keluaran (Output) Logika 1 jika semua masukan (Input) bernilai Logika 1 dan akan menghasilkan Keluaran (Output) Logika 0 jika salah satu dari masukan (Input) bernilai Logika 0. Simbol yang menandakan Operasi Gerbang Logika AND adalah tanda titik (“.”) atau tidak memakai tanda sama sekali. Contohnya : Z = X.Y atau Z = XY.

Tabel Kebenaran Gerbang AND (AND Gate)

Tabel Kebenaran Gerbang AND (AND Gate)

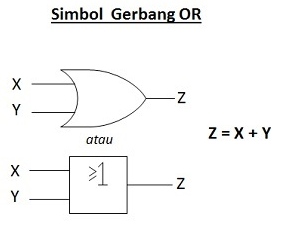

2. Gerbang logika OR

Gerbang OR memerlukan 2 atau lebih Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang OR akan menghasilkan Keluaran (Output) 1 jika salah satu dari Masukan (Input) bernilai Logika 1 dan jika ingin menghasilkan Keluaran (Output) Logika 0, maka semua Masukan (Input) harus bernilai Logika 0.

Simbol yang menandakan Operasi Logika OR adalah tanda Plus (“+”). Contohnya : Z = X + Y.

Simbol yang menandakan Operasi Logika OR adalah tanda Plus (“+”). Contohnya : Z = X + Y.

3. Inverter

Inverter berfungsi sebagai converter daya listrik yang mampu mengonversikan arus searah atau DC (Direct Current) menjadi arus bolak-balik atau AC (Alternating Current), atau juga sebaliknya dengan efektivitas yang sama. rangkaian inverter juga dapat dimanfaatkan untuk mengatur atau menstabilkan tegangan dari keluaran arus listrik yang dihasilkan.

4. IC 7432

4. IC 7432

Apabila semua / salah satu input merupakan bilangan biner (berlogika) 1, maka output akan menjadi 1. Sedangkan jika semua input adalah bilangan biner (berlogika) 0, maka output akan berlogika 0.

5. IC 7408

Apabila semua / salah satu input merupakan bilangan biner (berlogika) 0, maka output akan menjadi 0. Sedangkan jika semua input adalah bilangan biner (berlogika) 1, maka output akan berlogika 1.

3.teori

Generic array logic (GAL) dicirikan

oleh array AND yang dapat diprogram ulang, dan array ATAU tetap logika output yang dapat diprogram ulang. Ini mirip dengan perangkat PAL,

dengan perbedaan bahwa array AND tidak hanya dapat diprogram seperti halnya

pada perangkat PAL tetapi dapat diprogram ulang. Hanya itu saja dapat diprogram ulang beberapa kali. Ini dimungkinkan oleh penggunaan

listrik sel PROM yang bisa dihapus untuk

menyimpan pola pemrograman. Perbedaan lainnya adalah dalam penggunaan logika output yang dapat diprogram ulang, yang memberikan lebih banyak

fleksibilitas bagi perancang. Perangkat GAL digunakan macrocells logic output (OLMCs) pada output, yang memungkinkan perancang

untuk mengkonfigurasi output

baik sebagai

output kombinasi atau output terdaftar.

Gambar (a) dan (b) masing-masing menunjukkan representasi skematik blok perangkat

GAL dan arsitektur OLMC khas yang digunakan

dengan perangkat GAL. OLMC dari tipe yang ditunjukkan pada Gambar (b) dapat dikonfigurasikan untuk menghasilkan empat keluaran

yang berbeda tergantung pada input pilihan.

Ini termasuk yang berikut:

1. S1S0

= 00: mode terdaftar dengan output

RENDAH aktif.

2. S1S0

= 01: mode terdaftar dengan output

TINGGI aktif.

3. S1S0

= 10: mode kombinasional dengan output

RENDAH aktif.

4. S1S0

= 11: mode kombinasional dengan output

TINGGI aktif.

Kita

dapat melihat bahwa dua dari empat input ke multiplexer 4-ke-1 adalah output

kombinasi, dan dua lainnya adalah output terdaftar.

Juga, dari dua output kombinasional, satu adalah TINGGI aktif output sedangkan yang lainnya adalah output RENDAH aktif. Hal yang sama terjadi

dengan output terdaftar. Dari

empat input ke

multiplexer, yang muncul di output tergantung pada input pilihan. 2-ke-1 multiplexer memastikan bahwa hasil akhir juga tersedia sebagai umpan balik

ke array AND yang dapat diprogram.

Prinsip Kerja :

jika logicstate inverter berlogika 1 maka arus akan mengalir ke gerbang logika AND dan arus dari gerbang logika And akan dialirkan ke Gerbang Logika OR. pada simulasi rangkaian ini, kita harus menginputkan logika nya untuk masing - masing gerbang logika agar mendapatkan output yang diinginkan

Download Simulasi Rangkaian KLIK DISINI !!!!!

Download materi KLIK DISINI !!!!!

Download HTML Rangkaian KLIK DISINI !!!!!

Download data sheet 7408 KLIK DISINI !!!!!

[kembali]

[MENUJU AWAL]Download materi KLIK DISINI !!!!!

Download HTML Rangkaian KLIK DISINI !!!!!

Download data sheet 7408 KLIK DISINI !!!!!

[kembali]

Tidak ada komentar:

Posting Komentar